Sänker tröskeln för innovation

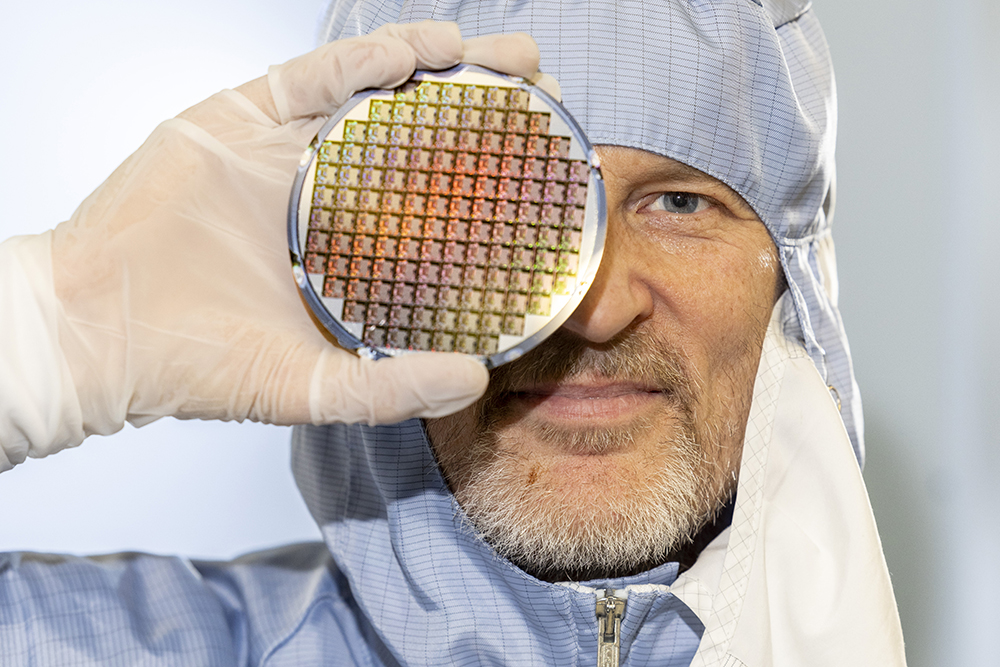

Att tillverka chip i en kommersiell produktionslina är både dyrt och ett statiskt förlopp som hämmar framsteg inom många forskningsområden. På Elektrumlaboratoriet i Kista arbetar Per-Erik Hellström med en annan lösning.

CMOS, eller chip, är en förutsättning för innovation inom många forskningsområden, från nanoteknologi till bioteknologi. För att producera dessa chip finns inga alternativ till kommersiella fabriker. Samtidigt är kostnaderna höga och tillverkningsprocessen erbjuder inget utrymme för experimentering med tekniken.

– Om du har stora volymer eller är ett stort teknikföretag är det inga konstigheter, men vill du tillverka tio chip är kostnaden på CMOS-linan alldeles för dyr, säger Per-Erik Hellström, forskare på KTH.

För att få ner kostnaderna väljer många så kallad heterogen integration, vilket innebär att andra tekniker som fotonik eller bioteknik integreras med chipen i produktionsprocessen. Tillvägagångsättet är bra, men dagens förutsättningar för det är långt ifrån optimala, menar Per-Erik Hellström.

– Fabrikerna vill sällan blanda in annan teknik i sina linor, så integrationen behöver ske i efterhand. Då blir det ofta lite ad hoc och med ett mischmasch av lösningar. Och det går ut över innovationen, säger han.

En billig och tillförlitlig lösning

På KTH:s Elektrumlaboratorium i Kista driver Per-Erik Hellström ett projekt som ska leverera en alternativ lösning – en mer tillförlitlig, tillgänglig och flexibel CMOS-lina på vilken användarna kan göra egna inställningar, integrationer och ändringar. Det gör det alltså möjligt adaptera elektroniken till det aktuella tillämpningsområdet direkt i tillverkningsflödet. Och det på ett sätt ett vanligt forskningsprojekt ska ha råd med.

Projektet, Heterogeneous integration with CMOS, drivs med stöd av SSF:s Research Infrastructure Fellows 2.

– Du ska kunna designa ditt chip och lita på att universitetet kan tillverka det. Det ger möjligheten att prova och testa olika koncept på ett sätt som inte är möjligt om du ska tillverka ditt chip i fabrik först. Det möjliggör extremt nischad elektronik för smalare tillämpningsområden och ger mycket bättre förutsättningar för innovationer.

Trots att projektet bara har ett år på nacken är arbetet redan långt fortskridet. Mycket tack vare försprånget från Per-Eriks arbete i tidigare SSF-projekt.

– Vi har fyra år kvar i det här projektet och har redan kommit till ett läge där vi integrerar CMOS-elektronik med saker som normalt sett inte ses som görbart.

Ett exempel är en forskarkollega i Uppsala som använder kedjan för att producera elektronik till en sensor för biokemisk detektering av väteatomer. En annan kollega arbetar med att integrera laser och detektorer för fotoner på chip.

Forskning tillämpad av forskare

Han berättar att stödet från SSF är avgörande, och på ett sätt inte helt självklart.

Tekniken i projektet var i forskningsfronten för 15 år sedan, då Per-Erik själv levererade publikationer i ämnet. På så sätt tillämpar han idag delar av sin egen tidigare forskning.

– Vårt projekt kommer inte att resultera i vare sig publikationer eller doktorander, vilket är produkten på ett universitet. Däremot hoppas vi såklart att samarbetena med andra forskare leder till det, säger han.

Och samarbetsmöjligheter finns överallt, menar han. Behovet av en CMOS-lina som denna är väldigt stort.

– Det finns fler tillämpningar än jag nästan kan komma på själv. Mitt mål är att vilken forskare som helst i Europa ska kunna arbeta med vår CMOS-lina, på ett kostnadseffektivt och tillgängligt sätt. Om man vill göra forskning som har ett värde av att få elektronik nära det man arbetar med, ska man absolut använda vår lina.

KTH – Heterogeneous integration with CMOS

Ett av sju projekt inom olika forskningsområden som finansieras genom SSF:s Research Infrastructure Fellows 2. Projektet verkar inom information, kommunikation och systemteknik och utvecklar tillverkningsteknologi och design för digital och analog CMOS. Drivs av Per-Erik Hellström vid KTH:s Elektrumlaboratoriet. Projektet pågår till och med 2027.

www.kth.se